Micron says new memory will break performance bottleneck

The semiconductor industry has spent years and untold dollars searching for a "universal memory" that could combine the performance of DRAM with the capacity and cost of flash. The recently-announced 3D XPoint, which was developed by Intel and Micron, isn't a universal memory--it isn't meant to fully replace either DRAM or NAND flash. But it does promise to combine many of their best features.

At the annual Linley Processor Conference this week, Micron's Todd Farrell explained how the two companies developed what he called the first truly new mainstream memory technology to come long in decades. He didn't shed much more light on the underlying technology, but he explained why the companies developed it and how it could deliver new levels of performance to everything from PC gaming to in-memory databases.

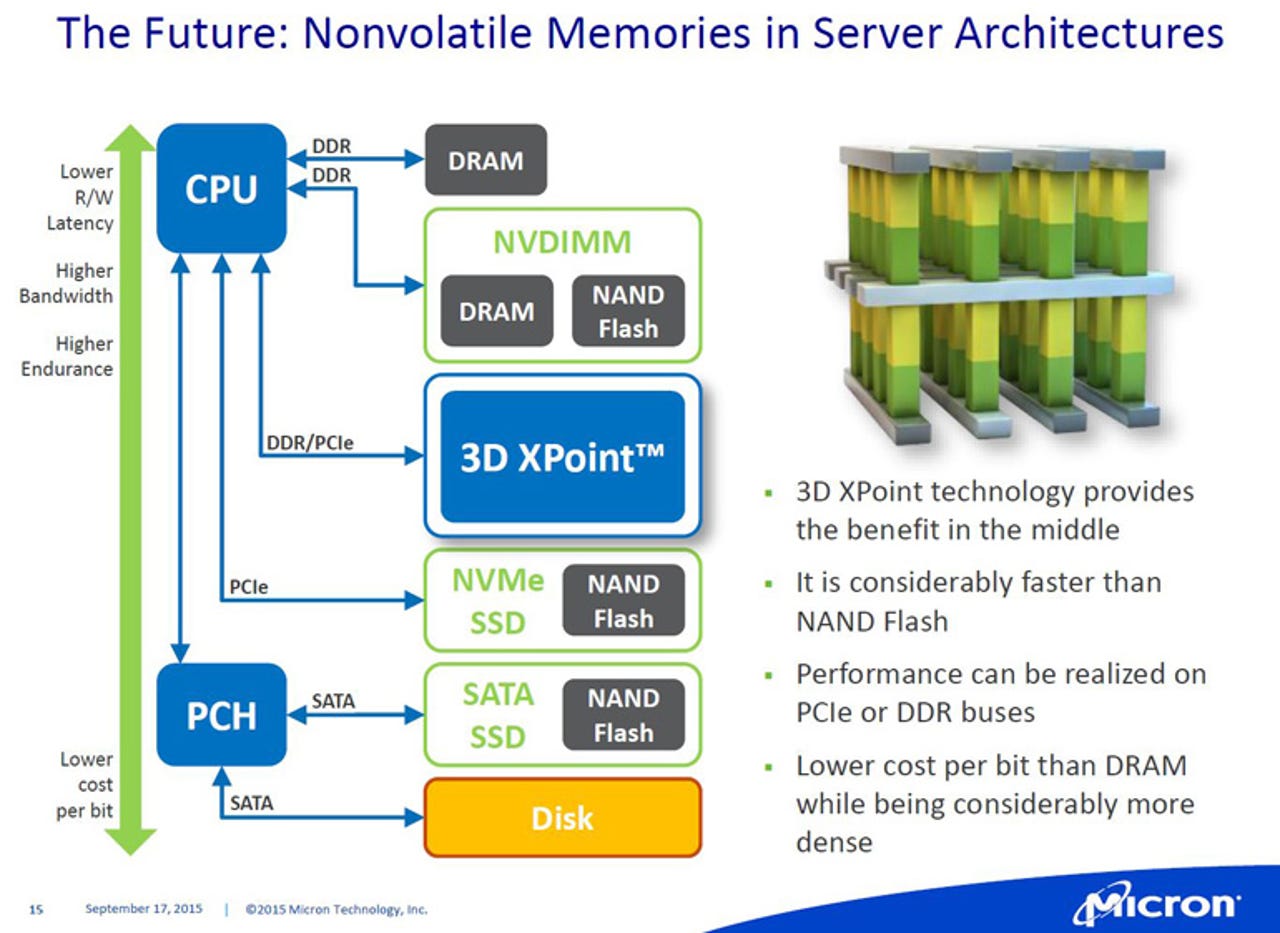

While there was lots of innovation in memory in the early days of computing, Farrell said that the last 25 years have been "fairly stagnant." DRAM density and cost per bit have largely plateaued, and while there has been significant growth in the capacity of NAND, the performance hasn't improved (in fact, it has arguably gotten worse). This has left a gap between system memory and storage. Solid-state drives have gotten faster thanks to new interfaces (NVMe on the PCI-Express bus and DDR), but so has DRAM with the introduction of DDR4, leaving wide gap. As processors continue to get faster, memory has become a performance bottleneck.

To address this, Micron has toyed with many emerging memory types. "I think we've probably looked at every item on the periodic table that is not radioactive in the search for an ideal memory," Farrell said. Many of these emerging memories such as phase-change memory (PCM) looked great on paper, but ultimately couldn't be manufactured in volume.

The difficulty of the challenge is understandable when you consider the requirements. The ideal memory needs to combines DRAM-like performance, byte-level addressability and low energy per bit combined with NAND-like density (a small memory cell size), persistence (non-volatile) and cost per bit. It also needs to be manufacturable on current process nodes (2Xnm or better) in existing 300mm fabrication facilities using available lithography tools. And it needs to have good industry support, meaning controllers and software that can take full advantage of a new tier of memory.

Both Intel and Micron claim that 3D XPoint is the first truly new memory to come along that meets the requirements. In comparison, to NAND flash, it is 1,000 times faster and has 1,000 times better endurance. It still isn't quite as fast as DRAM, but it is 10 times denser and costs much less. The active power consumption is competitive with what we have today, and since it is non-volatile, it doesn't need to be continually refreshed like DRAM.

What we know about 3D XPoint is that the memory cells use some sort of material that changes its properties in a cross-point array that provides bit-level addressing and can grow vertically to increase density. The first 3D XPoint device, a dual-layer 128GB chip manufactured at the joint IM Flash fab in Lehi, Utah, will be available sometime next year. Farrrell said that multiple 3D XPoint technologies are in development and "showing promise." These devices will work over both the DDR and PCIe bus, noting that Intel has already announced it will have direct support for 3D XPoint in their processors with something like a DDR interface.

The primary target for 3D XPoint is "massive in-memory databases," but it could be used in any application that requires a large pool of high-performance memory such as RAID storage systems, meta-data storage, system backups, storage tiering and server cache, data logging and de-duplification. It is likely to be adopted in industries that need low latency such as oil & gas, financial transactions and genomics. Farrell also mentioned gaming and high-fidelity pattern recognition as possible markets.

Micron sees a long road ahead for its conventional memory. It is ramping 20nm DRAM, and Farrell said there will be at least three more nodes with 1Xnm development underway in Taiwan, and 1Ynm and 1Znm development taking place in the U.S. In NAND flash, Micron is ramping 16nm TLC (Triple-Level Cell or three bits per cell, which increases capacity) and is on track for 3D NAND production in Singapore next year. On the company's quarterly earnings call last week, CEO Mark Durcan said 3D NAND will be the majority of NAND flash production by late 2016.

The first products to use HMC, including high-end networking gear for telecommunications and cloud data centers and supercomputers, should start showing up next spring. Juniper has already announced that it will use HMC in its Q5 ASIC and QFX10000 switch to break the 1Tbps barrier. Intel will also be using a variant of the HMC in its Knights Landing processor for high-performance computing.