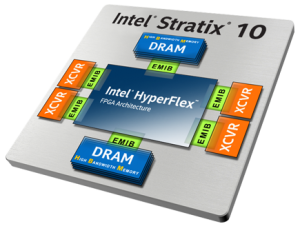

With densities greater than 1 million logic elements (MLE), Intel Stratix 10 SX FPGAs provide the flexibility and low latency benefit of integrating an ARM processor with a high-performance, high-density FPGA needed to tackle the design challenges of next-generation, high-performance systems.

By integrating the FPGA and the ARM processor, Intel Stratix 10 SX FPGAs arevsuitable for 5G wireless communication, software defined radios, secure computing for military applications, network function virtualization (NFV), and data center acceleration.

For NFV applications that consolidate and deliver the networking components needed to support a fully virtualized infrastructure, Intel Stratix 10 SX FPGAs can handle the high-speed data path while integrated processors enable low latency transactions needed to manage flow tables for control plane processing.

With hardware acceleration, Intel Stratix 10 SX FPGAs provide a heterogeneous computing environment to create optimized, low latency accelerators. In secure computing applications, integrated processors make it much more difficult to snoop software operations thereby keeping data secure. These devices also enable general purpose utility processing to extend convenience and form factor reduction in high end systems.

Customers can implement their designs today with Intel Stratix 10 SX, using the Intel SoC FPGA Embedded Development Suite (SoC EDS), a comprehensive tool suite for embedded software development. It comprises development tools, utility programs, and design examples to jump-start firmware and application software development.

The SoC EDS also enables customers to utilize the ARM* Development Studio 5* (DS-5*) Intel SoC FPGA Edition to code, build, debug, and optimize their application

Electronics Weekly Electronics Design & Components Tech News

Electronics Weekly Electronics Design & Components Tech News